前言

今天天气阴沉,刚才又下起了小雨,温度骤降,前几天脱下的秋裤,今天又穿上了,这天气真是变化无常。上周六(4.20)参加了一场关于RSIC-V的技术沙龙,第一次真正了解了RISC-V架构,正好今天不打算出门,准备总结一下这次研讨会,也了解一下RISC-V这种架构。我是上周四(4.18)在公众号【嵌入式系统资讯精选】看到说周六会在北航举办一个RISC-V的技术沙龙,正好周末也没有其他的安排,所以就直接报名参加了。一路公交转地铁,终于赶到了北航,从东南门直接进去,之前去过一次北大,还需要提前预约才能进去,而北航则可以直接进去。首先进行了签到,然后可以领取一本最新一期的【单片机与嵌入式系统应用】杂志,之前还没看过这个杂志,开始之前看了一下,内容主要是最新的技术论文。

关于嵌入式系统联谊会

由国内知名学者和产业人士共同发起的嵌入式系统联谊会,于2008年底在北京正式成立。嵌入式系统联谊会为中国嵌入式系统不同学科领域的专家学者、工程技术人员、市场人士和科技媒体人士提供学术和产业信息交流的环境,是增进个人友谊的科技沙龙性质机构。嵌入式系统联谊会主题讨论会自2009年开始,已经召开19次会议,会议反响热烈,参加总人数已经累计超过千人次,见诸媒体的报道百余篇。联谊会作为嵌入式系统学术界、产业界、科技媒体的交流和联系平台的作用和定位得到广泛认可。嵌入式系统联谊会是九十年代末成立的北京单片机联谊会的延伸。历次会议议题和演讲题目请跳转至论坛回顾页。

何小庆(嵌入式系统联谊会秘书长)

RISC-V架构简介

RISC-V(发音同“risk-five”)是一种免费开源指令集架构(ISA),通过开放标准协作开创处理器创新的崭新纪元。RISC-V基金会创立 于2015年,由超过235家成员组织组成,建立了首个开放、协作的软硬件创新者社区,开创了处理器创新的新时代。RISC-V ISA发端于深厚的学术研究,将免费且可扩展的软硬件架构自由度提升至新的水平,为未来50年的计算设计与创新铺平了道路。

现在处理器的指令集主要分为RISC和CISC,即精简指令集和复杂指令集,RISC的代表就是著名的ARM架构,专注于高性能,低功耗,小体积,主要应用于移动设备;而CISC的代表是x86架构,像常用的PC、服务器的CPU等等,专注于桌面,高性能和民用市场。而RISC-V是属于RISC阵营的,相比于ARM,RISC-V的历史很短,2010年诞生于加州大学伯克利分校,当时的Krste Asanovic教授希望寻找一个合适的CPU指令架构,但x86架构复杂臃肿、ARM架构需要授权费、开源的OpenRISC架构又太老旧了,所以他最终决定自己做个开源CPU架构,并在2015年成立了RISC-V基金会(RISC-V Foundation ),专门推动RISC-V发展,现在的RISC-V基金会成员也超过了235个,包括国外的Google、三星、英伟达、微芯、高通、惠普、意法半导体、西数、NXP,国内的阿里巴巴、华为、高云等公司。

会议总结

RISC-V嵌入式开发技术沙龙宣传海报:

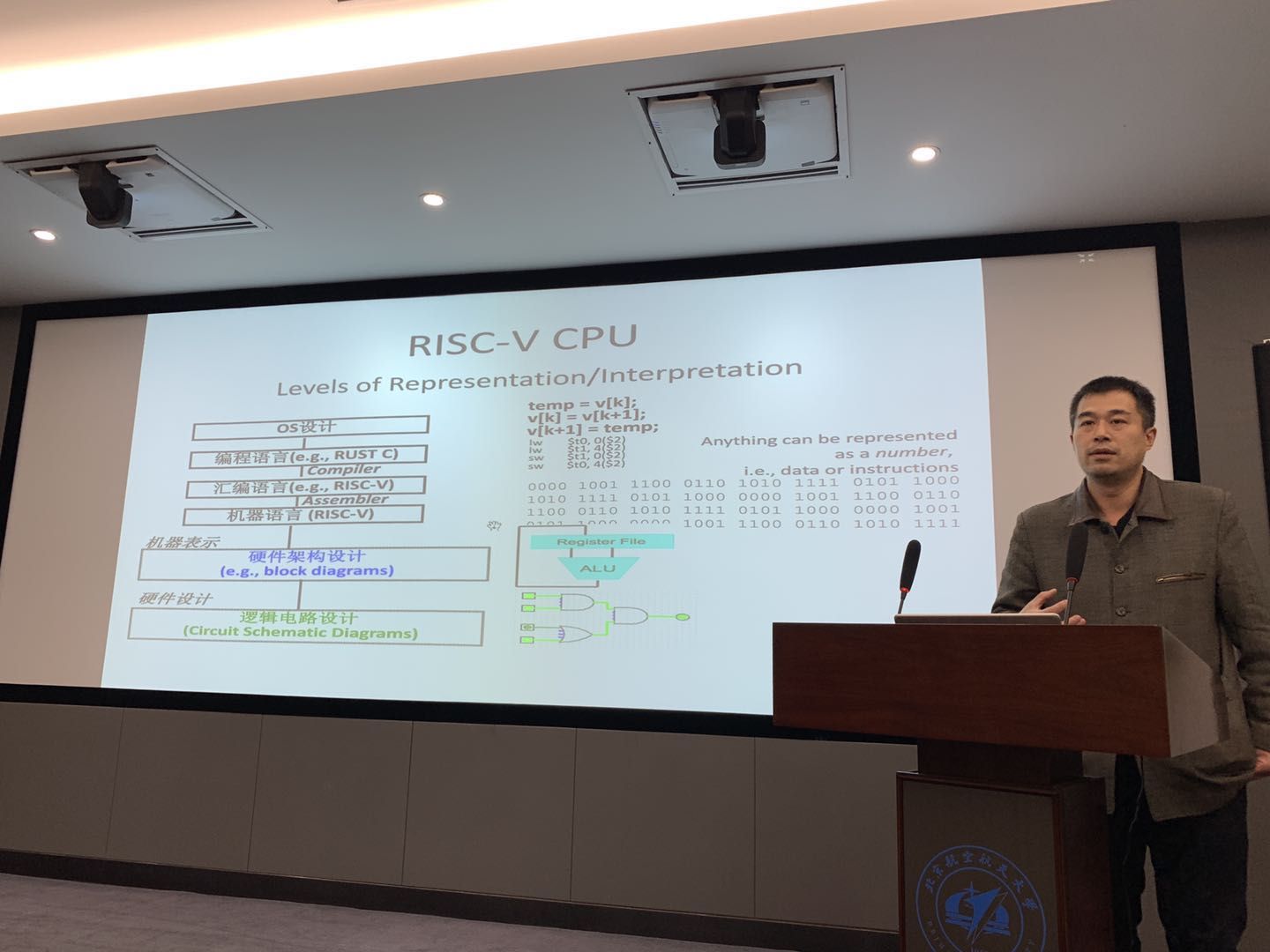

陈渝——基于RISC-V的操作系统课程

身为研究操作系统的老师,陈渝认为,RISC-V精简指令集听起来属于硬件范畴,但是其实RISC-V与软件有很大的相关性,因为作为重要系统软件的操作系统负责对硬件进行管理和控制,以实现对上层应用的支持。陈老师介绍,不同学校计算机系对操作系统课程教学的要求存在差异,有的只要求会用,有的却需要懂得操作系统。清华大学的操作系统课程目标是希望学生能够用一种高级语言在某一种CPU上实现操作系统的设计。陈老师在多年的操作系统教学实践中,一直在做不同的尝试,比如在x86、MIPS、Arm上实现,直到2017年,发现RISC-V是一个很不错的选择。RISC-V本身来源于学校,已经经过长期的探索,而且它是开源的,学生可以接触到关于它的所有信息(不像x86和Arm,很难深入了解更多细节),所以更容易在其上开发应用软件和操作系统。关于为什么选择RUST作为RISC-V的开发语言,陈老师这样解释:虽然现在大多数的操作系统选用C语言开发,但是还是存在潜在的安全问题,所以目前国外很多学校也都在探索使用C语言之外的语言做开发,比如MIT尝试使用Go语言。鉴于RUST不仅有严格的安全约束,可以把编译时约束转移到运行时,而且允许程序员显式地指出不安全(unsafe块),并使用安全封装和管理不安全,所以才选择了RUST。经过两年的教学实践,陈老师表示在RISC-V上开发操作系统还是非常有优势的,比如有的同学在32位环境下开发的系统,只需要微小的改动(一两天的工作量)就可以移植到64位上,说明RISC-V在硬件架构设计上已经做了软件的一致性考虑。

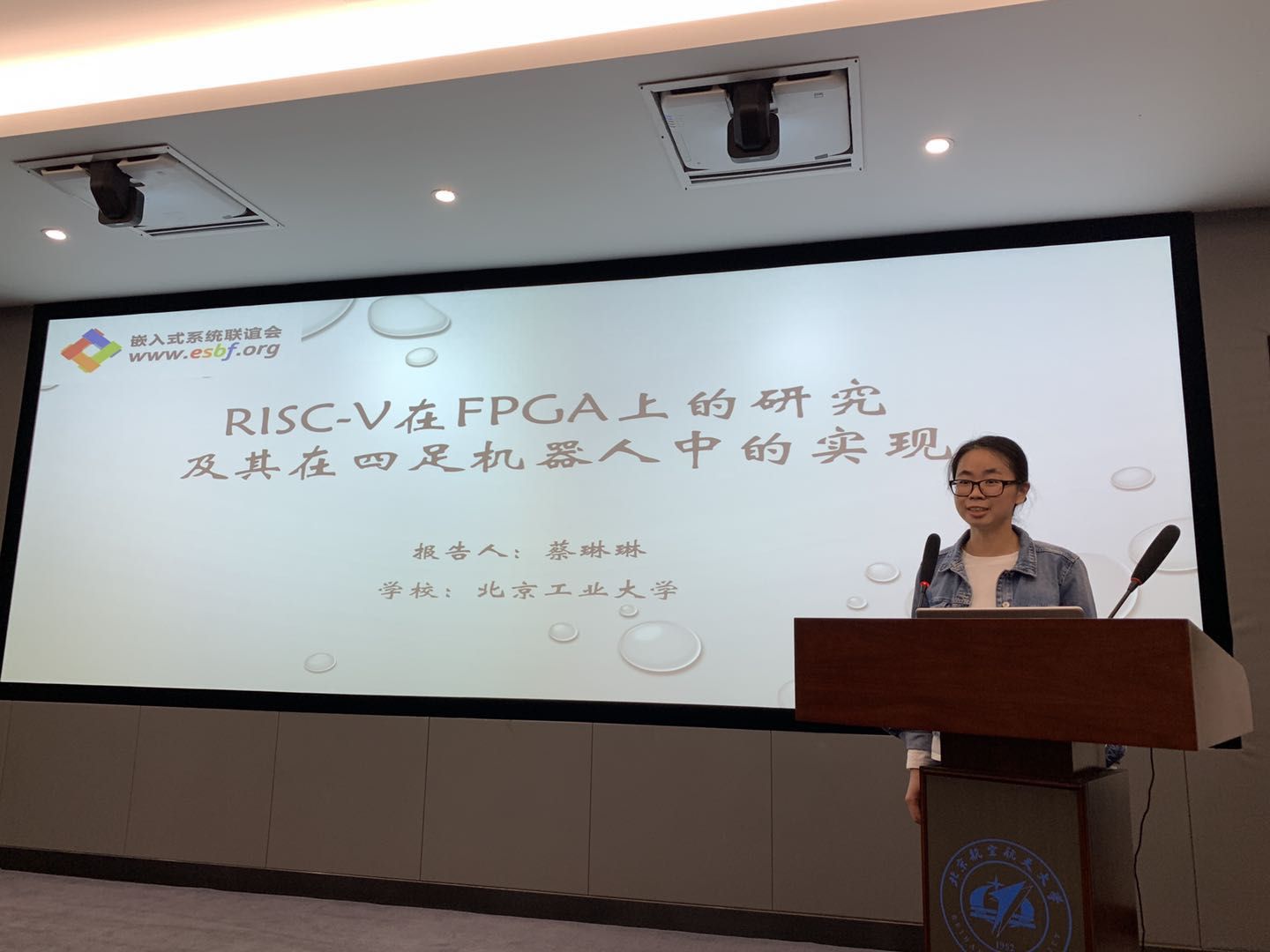

蔡琳琳——基于RISC-V架构处理器实现的四足机器人

来自北京工业大学的硕士研究生蔡琳琳,演示了基于RISC-V处理器架构实现的四足机器人,控制芯片使用的Xilinx 的 Artix-7 FPGA 芯片,Xilinx 的 Artix-7 技术具有低功耗和高性能,其支持 RISC-V 软架构的能力使其成为便携式设备的理想选择。使用的芯片型号是XC7A100T-1CSG324I,熟悉FPGA芯片的朋友,应该能看出来,100T说明内部有100K的逻辑单元可用。内嵌了RISC-V的软核,换句话说,就是可以把它当成一个RISC-V内核的MCU来用,而且,由于FPGA每个引脚都可以进行定制,所以这个处理器的PWM通道、串口等外设的数量可以根据自己的需要来进行定制。最后,进行了实际的控制演示,包括前进、后退、转弯、匍匐运动等等。

胡振波——RISC-V架构嵌入式开发的特点

胡振波是国内最早开始研究RISC-V架构的,有超过8年的CPU以及超过10年的ASIC设计与验证经验,历任Marvell CPU高级设计工程师,Synopsys ARC系列处理器内核研发经理等职务,有着近20年的行业积累。发言结束后,会上有一位与非网的朋友提问到,“作为国内RISC-V处理器研究的领导者,芯来科技为什么没有选择做芯片而是做IP核呢?”胡振波给出的答案是,“国内现在已经有近2000家芯片公司,如果我们选择做芯片,只是众多芯片公司中的2000分之一,现在基本是国外公司SiFive在做基于RISC-V架构的IP,国内公司对底层技术掌握的很少,本土的公司能做IP的也很少,如果没有人来做IP,就会变成从ARM垄断的ARM架构市场转为SiFive垄断的RISC-V架构的市场,我们放弃做芯片,专注做IP,服务国内其它商业公司。虽然芯来科技从创立到现在只有半年的时间,我们开发的IP已经导入国内很多龙头公司的产品中,这样做最终为本土产业带来更大的帮助,这种选择大于我们做芯片的意义。我们选择了看似不是被人理解的方向,是为了更好帮助本土IC产业发展,算是间接实现个人的自我价值。”

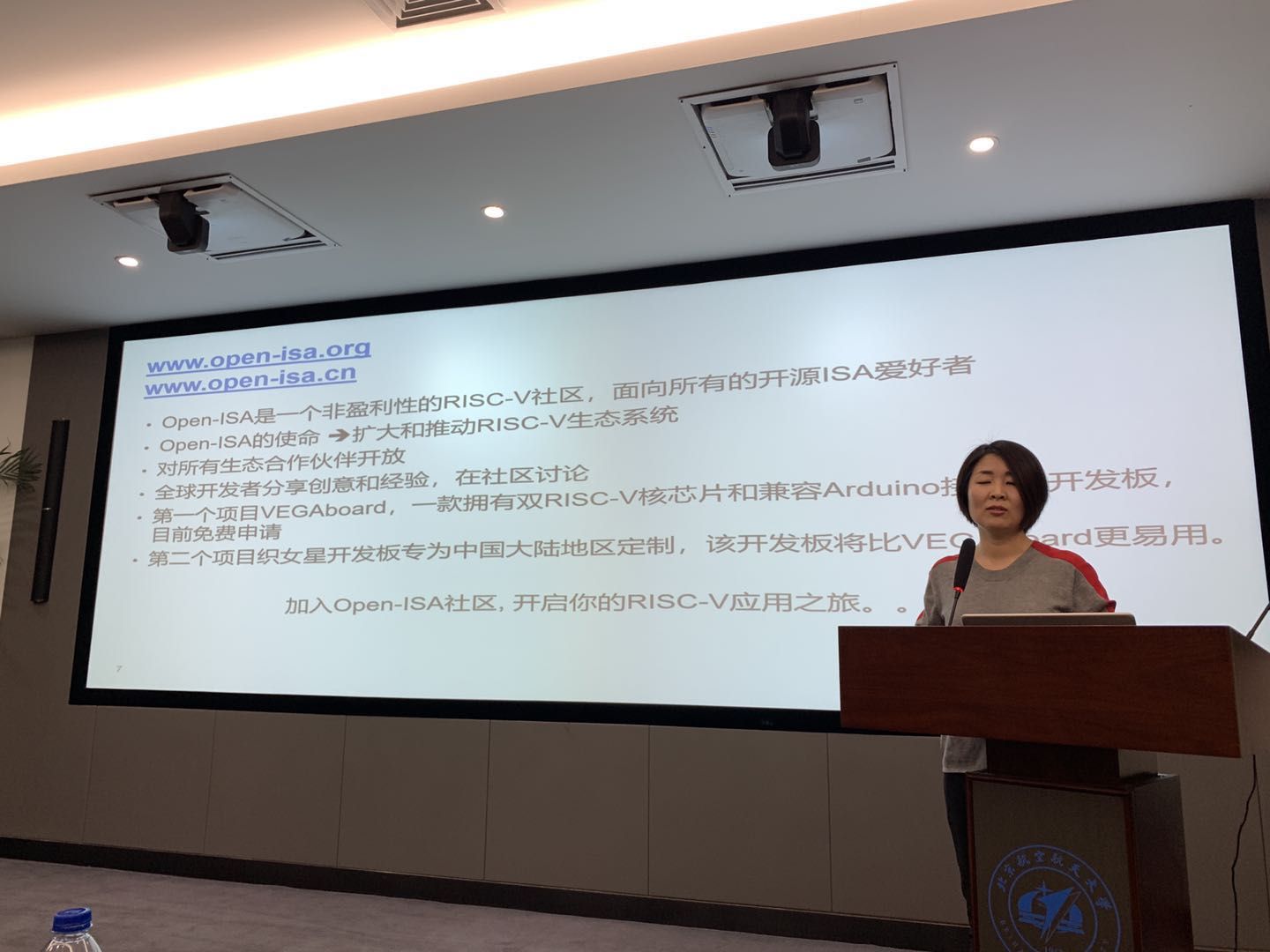

王朋朋——RISC-V的发展需要完善的生态系统

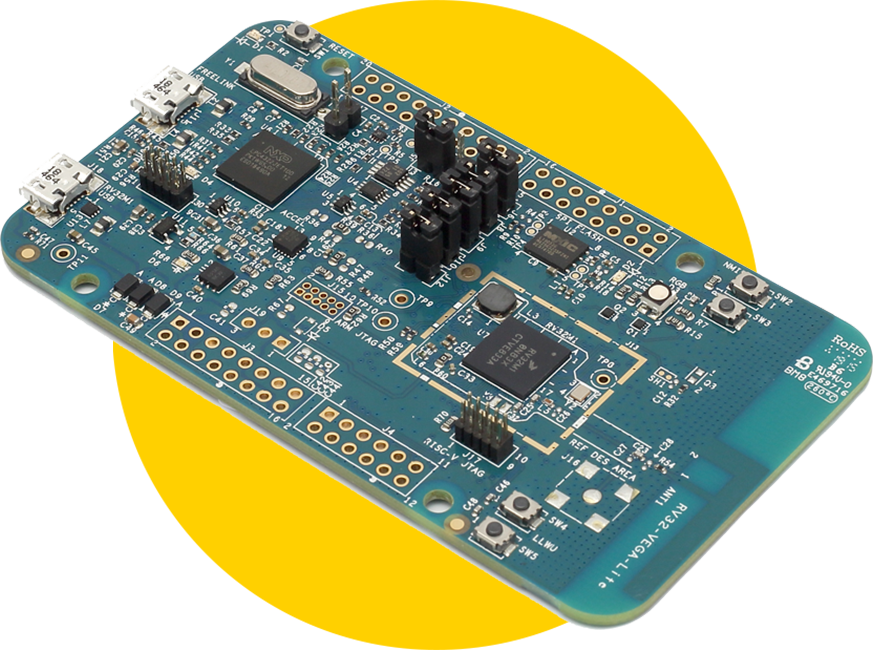

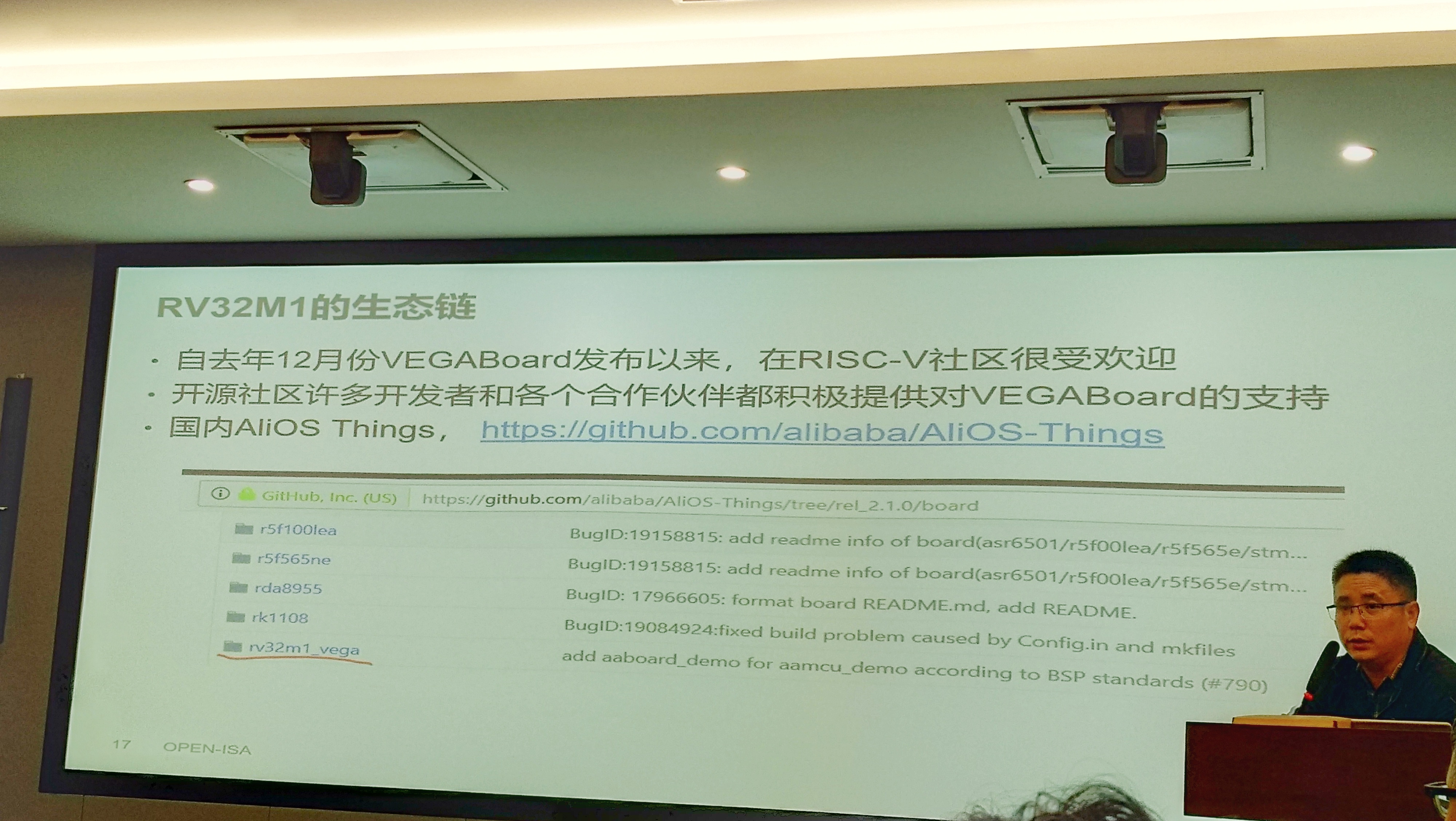

恩智浦NXP的系统工程总监王朋朋,RISC-V的发展,需要的是完整的生态系统,IP核、芯片、IDE、开发板、文档资料、社区论坛等等,据王朋朋介绍,NXP内部RISC-V技术的发展主要是软件部门在推动,而不是芯片部门,可见,NXP非常看重软件方面的深度。会上,又介绍了NXP研发的4核性能怪兽RV32M1芯片,它包含两个RISC-V内核和两个ARM内核,而且已经开发了配套的开发板VEGA织女星开发板,如图

标准版

中国版

可以看出,国际标准版本和中国版本还是有一些区别的,具体的信息可以访问官方网站:OpenISA,中文网站:OpenISA,今年5月份会举办一个创意竞赛,开发者可以免费申请一块VEGA织女星开发板,并完成一些创意设计,优秀者可以或者一定的奖品,有需要的朋友可以登陆论坛申请。时间安排:

刘华东——RSIC-V MCU的嵌入式开发

NXP高级工程师刘华东,介绍了RV32M1配套的IDE,基于GNU GCC RISC-V交叉工具链配合Eclipse集成开发环境,调试软件采用OpenOCD,只要所连接的硬件调试器支持标准的JTAG协议,就可以直接使用。开发环境下载:下载专区,从官方提供的SDK和工具链可以看出,支持Windows、Linux和Mac系统,可以适用于使用不同操作系统的开发者。

在介绍了恩智浦推出的VEGAboard和织女星开发板之后,刘华东又详细介绍了RV32M1内核,这是一个异构4核MCU,包括两个RISC-V内核(一个RI5CY核和一个ZERO_RISCY核)以及两个ARM内核(一个Cortex-M4F核和一个Cortex-M0+核),单芯片就可运行BLE、Mesh/Thread/ZigBee协议,特别适合于超低功耗的移动设备。由RV32M1的架构可见,RISC-V与Arm其实并非互斥关系,两者相互融合之后,完全有可能碰撞出更大的火花!

盛磊——支持RISC-V的专业开发工具IAR

IAR,将于5月发布1.0 Beta版本,将会支持RSIC内核MCU,计划6月份推出1.10商用版本给合作客户,并且后续还会推出升级版本,后续版本会着重优化代码体积和执行速度。

直播回看

直播回看:RISC-V架构嵌入式开发研究与实践

相关资讯

- 2018年9月17日,华米正式发布可穿戴领域全球首颗RSIC-V芯片——”黄山一号”

众所周知,作为小米生态链的一员,小米手环的开发公司,华米公司开发了多款手环,手表等穿戴设备。黄山一号已经流片成功,内部测试较ARM Cortex-M4运算效率高出38%,商用时间为2019年上半年,让我们拭目以待。

- 西数首发RSIC-V架构的SSD主控芯片:28nm工艺、1.8GHz主频

西数目前的SSD及HDD硬盘主控芯片多是Marvell提供的,芯片内核是ARM的Coretex系列,但是西数 去年就公布过RISC-V路线图,未来会在这些领域用RISC-V架构的处理器取代ARM处理器,西数每年大约使用10亿颗芯片,未来这些芯片都会从ARM转向RISC-V体系。

声明

文中部分图片来自【嵌入式系统联谊会】微信交流群,版权归嵌入式系统联谊会所有。如果侵权,请联系删除。

参考资料

本文部分内容参考以下文章,非商业目的,如有侵权,请联系我删除。

- VEGA Board 官方网站

- 嵌入式系统联谊会官网

- RISC-V Foundation基金会网站

- 是什么原因,让华米科技花了三年的时间打造“黄山1号”?

- RISC-V要发展,不是芯片起主导作用,而是生态系统

- RISC-V当真是中国处理器产业的最后一次机会?

- 胡振波:我的芯片之路

历史精选

- Jlink使用技巧系列教程索引

- Keil报错:cannot open source input file “core_cmInstr.h” 解决办法

- 基于uFUN开发板的RGB调色板

- 基于uFUN开发板的心率计(三)Qt上位机的实现

- Qt实现软件自动更新的一种简单方法

欢迎关注我的个人博客:www.wangchaochao.top

或微信扫码关注我的公众号