SPI协议简介

板卡内不同芯片间通讯最常用的三种串行协议:UART、I2C、SPI,之前写过串口协议及其FPGA实现,今天我们来介绍SPI协议,SPI是Serial Perripheral Interface的简称,是由Motorola公司推出的一种高速、全双工的总线协议。

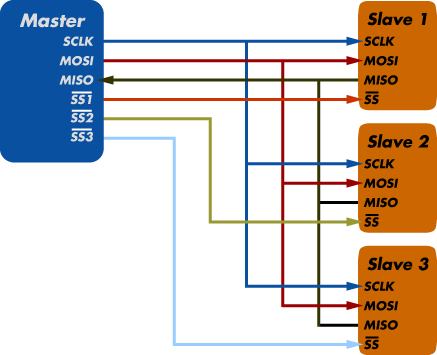

与IIC类似,SPI也是采用主从方式工作,主机通常为FPGA、MCU或DSP等可编程控制器,从机通常为EPROM、Flash,AD/DA,音视频处理芯片等设备。一般由SCLK、CS、MOSI,MISO四根线组成,有的地方可能是:SCK、SS、SDI、SDO等名称,都是一样的含义,当有多个从机存在时,通过CS来选择要控制的从机设备。和标准SPI类似的协议,还有TI的SSP协议,区别主要在片选信号的时序上。

4线还是3线?

当我们谈到SPI时,默认情况下都是指标准的4线制Motorola SPI协议,即SCLK,MOSI,MISO和CS共4根数据线,标准4线制的好处是可以实现数据的全双工传输。当只有一个主机和一个从机设备时,只需要一个CS,多个从机需要多个CS,各数据线的介绍:

- SCLK,时钟信号,时钟频率即SPI速率,和SPI模式有关

- MOSI,主机输出,从机输入,主机数据

- MISO,主机输入,从机输出

- CS,从机设备选择,低电平有效。

3线制SPI,根据不同的应用场景,主要有以下2种类型:

- 只有3根线:SCLK,MOSI和CS,没有MISO数据线,适用于单工通讯,主机只发送或只接收从机的数据。

- 只有3根线:SCLK,SDIO和CS,这里的SDIO作为双向端口,适用于半双工通讯,比如ADI的多款ADC芯片都支持双向传输。在使用FPGA操作双向端口时,作为输入时要设置为高阻态z。

还有标准SPI协议的升级版,Dual SPI、Quad SPI和QPI等,这些协议不在本小节3线/4线制讨论的范围内,文章后面会提到。

4种工作模式

既然是进行数据传输,双方就要明确从机在什么时刻去采样主机发出的数据,主机在什么时刻去读取从机发来的数据。对于STM32等MCU自带的硬件SPI外设来说,可能没有那么重要,只需要配置一下模式就行了,但是对于使用使用GPIO模拟或者FPGA来实现SPI的时序,这一点是非常非常重要的,这就涉及到SPI标准协议的工作模式了,通过CPOL(Clock Polarity)时钟极性和CPHA(Clock Phase)时钟相位的不同组合,可以分为4种模式。

一般从机器件的工作模式是固定的,主机需要采用一样的工作模式,双方才能正常“交流”。

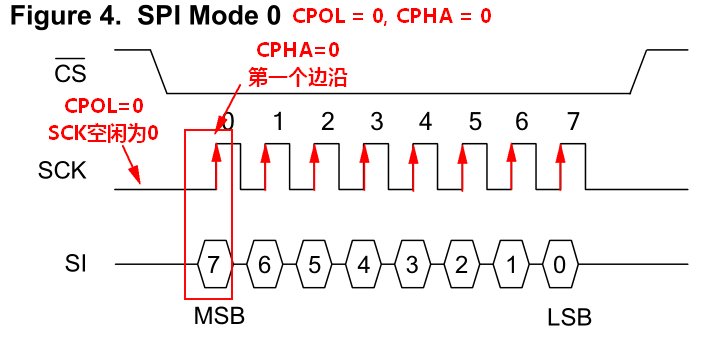

CPOL=0表示,SCK在空闲状态时为0

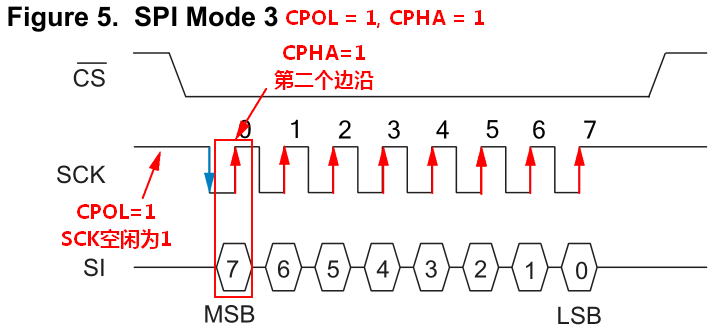

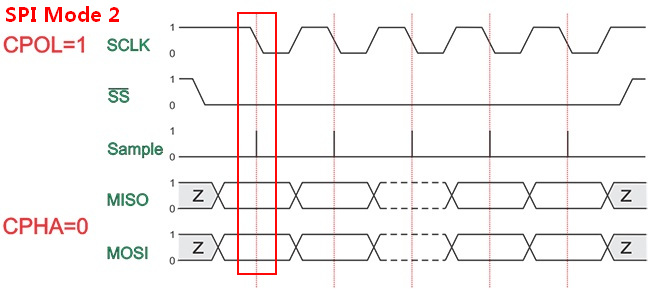

CPOL=1表示,SCK在空闲状态时为1

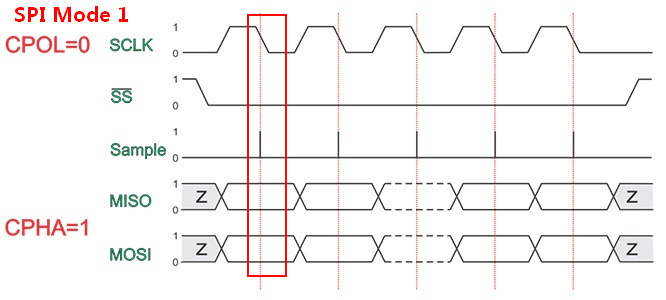

CPHA=0表示,在SCK第一个边沿时输入输出数据有效

CPHA=1表示,在SCK第二个边沿时输入输出数据有效

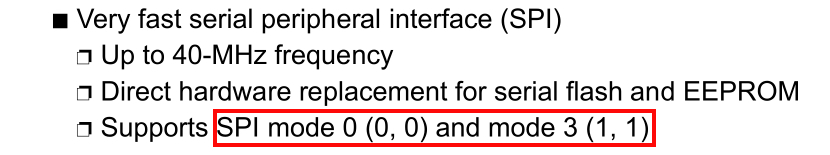

这四种模式中,应用最广泛的是模式0和3,大多数SPI器件都同时支持这两种工作模式,其实这些都不重要,具体采用什么模式,看你的器件手册就知道了。

以我最近工作中使用到的一款Cypress的铁电存储器FM25V05为例,在其官方DataSheet上介绍同时支持SPI Mode 0和Mode 3,

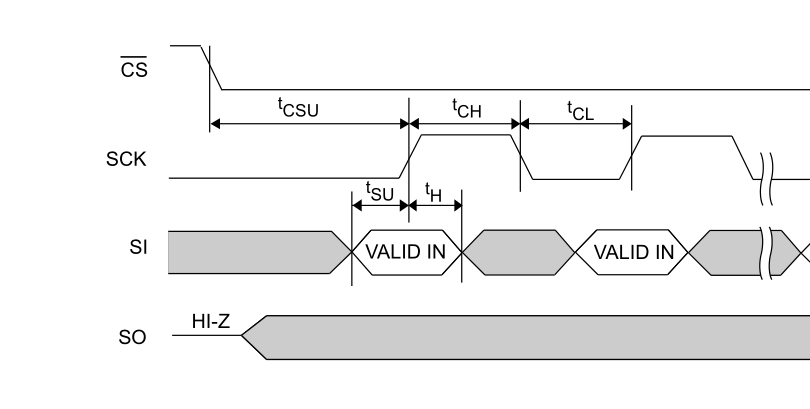

根据后面的时序图,可以得知SPI mode 0的读写时序,图中可以看出SCK空闲状态为低电平,主机数据在每个上升沿被从机采样,数据输出同理。

对于SPI mode3,SCK空闲状态为高电平,主机数据在每个上升沿被从机采样,数据输出同理。

模式1和模式2同理,模式1即CPOL=0,CPHA=1,SCK空闲为0,在SCK第二个边沿时数据有效,即SCK下降沿有效。

模式2即CPOL=1,CPHA=0,SCK空闲为1,在SCK第一个边沿时数据有效,即SCK下降沿有效。

在一些自带SPI硬件外设的MCU上,设置主机的SPI模式非常简单,只需要配置几个寄存器的值即可,而且是写了SCK高电平还是低电平,和第一个还是第二个边沿,不用去记忆等于0还是等于1。以STM32F103硬件SPI配置为例:

SPI_InitTypeDef SPI_InitStruct;

SPI_InitStruct.SPI_Mode =SPI_Mode_Master; //主

.....

SPI_InitStruct.SPI_CPOL =SPI_CPOL_High; //SCK空闲时为高电瓶

SPI_InitStruct.SPI_CPHA =SPI_CPHA_1Edge;//SCK第一个边沿有效

.....

SPI_Init(SPI2,&SPI_InitStruct);

而在FPGA中实现,需要严格根据时序来控制SCK和数据的输入输出。

多种传输速率

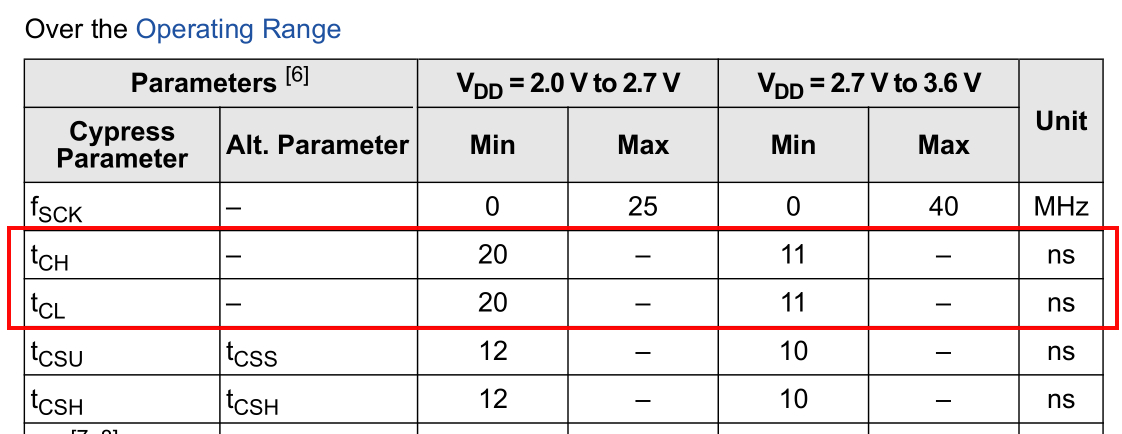

SCK的速率就是SPI的传输速率,SPI协议没有一个固定的速率,不像IIC标准模式100K,快速模式400K,高速模式3.4M,SPI的传输速率取决于器件本身支持多高的速率,器件手册里都有描述,以FM25V05铁电EPROM为例:

不同电源电压情况下的最大SCK时钟频率:

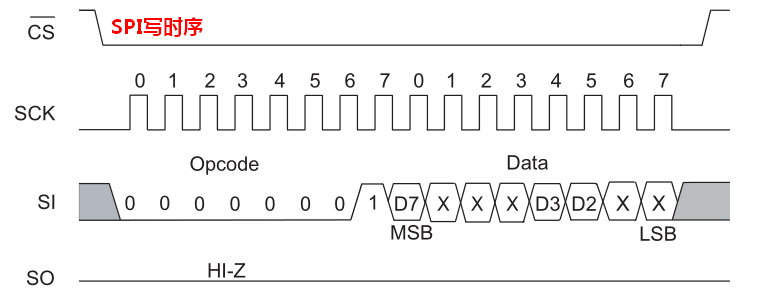

SPI协议的基本时序

CS为低电平时,表示对应的从机设备被使能,在每个SCLK周期可以传输1Bit数据,采样时刻取决于器件支持的SPI mode,根据不同SPI器件的控制方法,在进行正式的数据读写操作前,一般需要先写入控制字,然后是寄存器地址和数据。下图是FM25V05铁电存储器采用SPI模式0的写时序:

读时序:

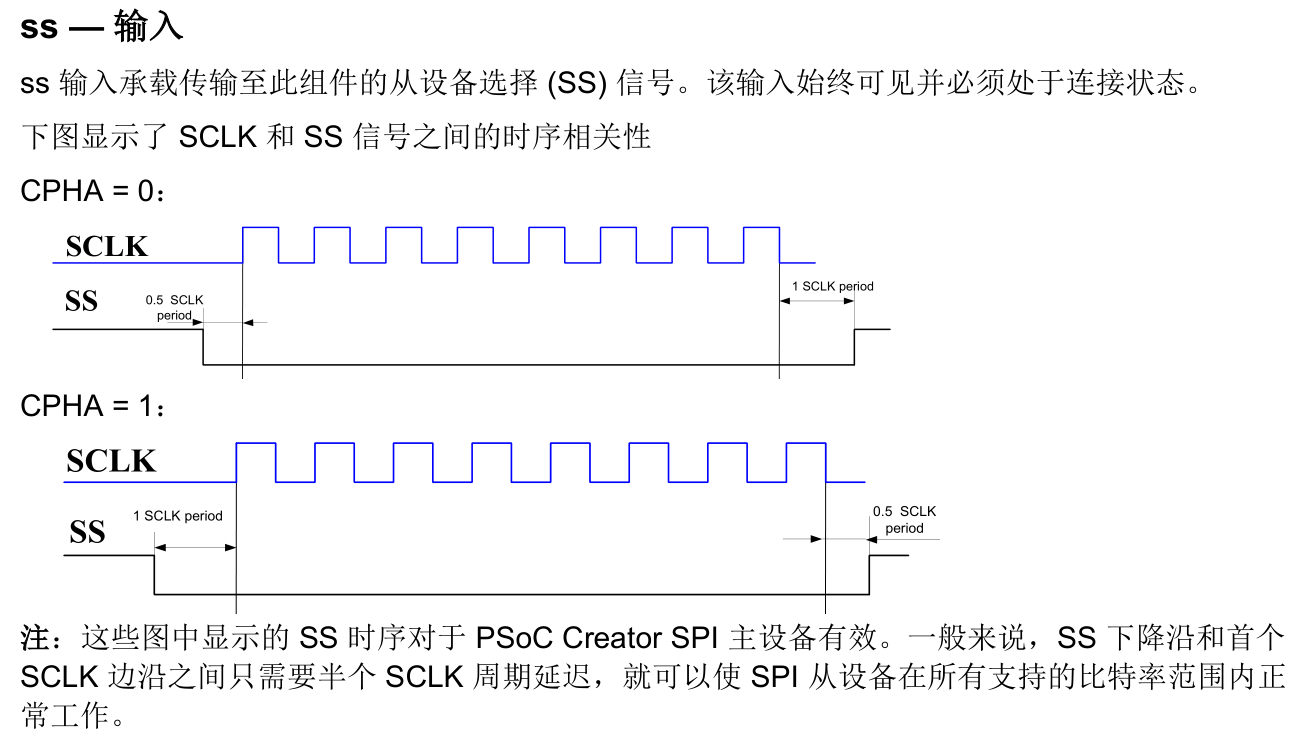

如果要使用FPGA来实现SPI时序,在CS下降沿和SCLK第一个边沿,或CS上升沿和SCLK最后一个边沿之间要留有一定的延迟时间,一般是0.5个SCLK周期。

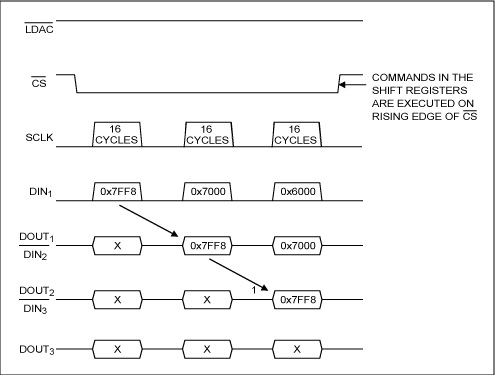

一些SPI从机设备支持菊花链连接模式,即节省GPIO,又不会占据太多布线面积,但并不是所有的SPI器件都支持菊花链模式。

控制时序:

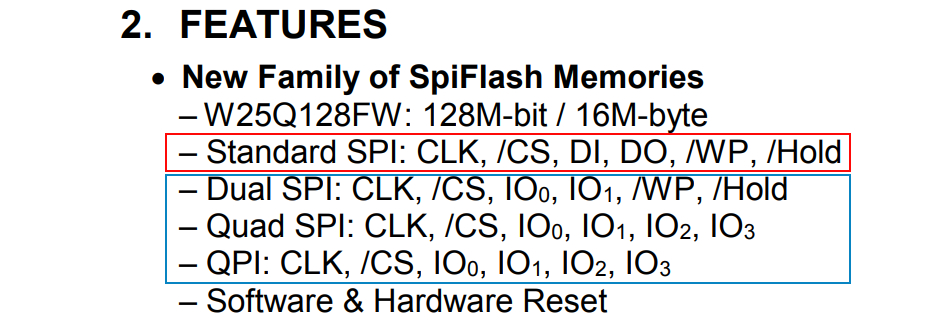

SPI协议的升级版

传统标准的SPI协议,一个SCLK周期只能传输1Bit数据,能不能一个SCLK传输多个Bit数据呢?答案是可以的。Motorola公司在现有的标准4线SPI协议上,又开发出了多种SPI协议的升级版,通过增加数据线位数的方式,来提高数据传输的效率,目前很多Flash厂家都已经支持多种SPI协议。

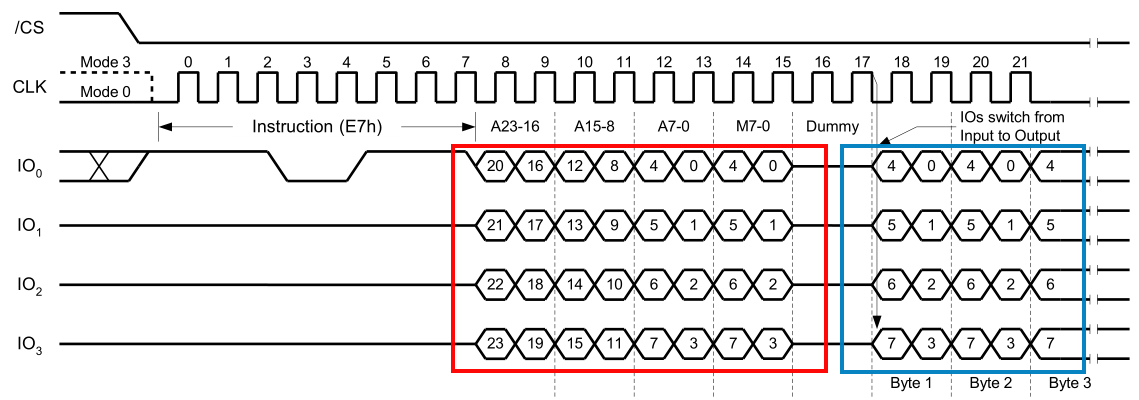

以比较常用的一款SPI Flash ROM W25Q128FW为例,在其器件手册上写着除了标准的4线SPI模式,还支持Dual SPI,Quad SPI,QPI等,在这几种模式下,IO0/1/2/3这些IO作为双向端口,大大增加了数据读写的速率。

QSPI协议读写时序:

一些支持QSPI协议的Flash芯片型号:

FPGA实现SPI协议

FPGA实现UART、SPI、IIC等串行时序,最常用的就是状态机大法,将各个步骤分解为各个状态,然后根据不同的状态去控制输出或读取输入,细节方面需要考虑数据的对齐、建立和保持时间、一些异常情况时状态的跳转,不能进入死循环,或卡死在某一个状态。

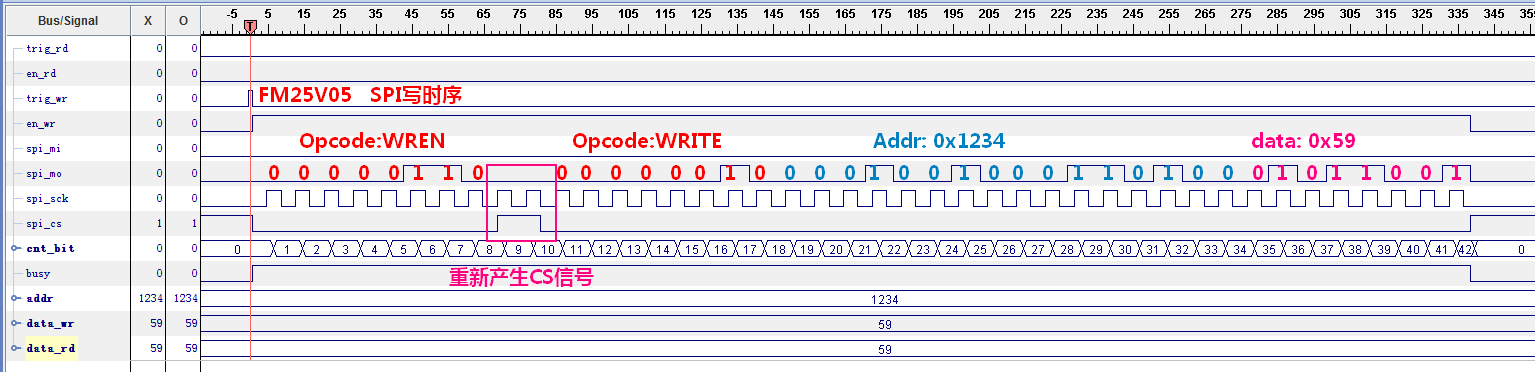

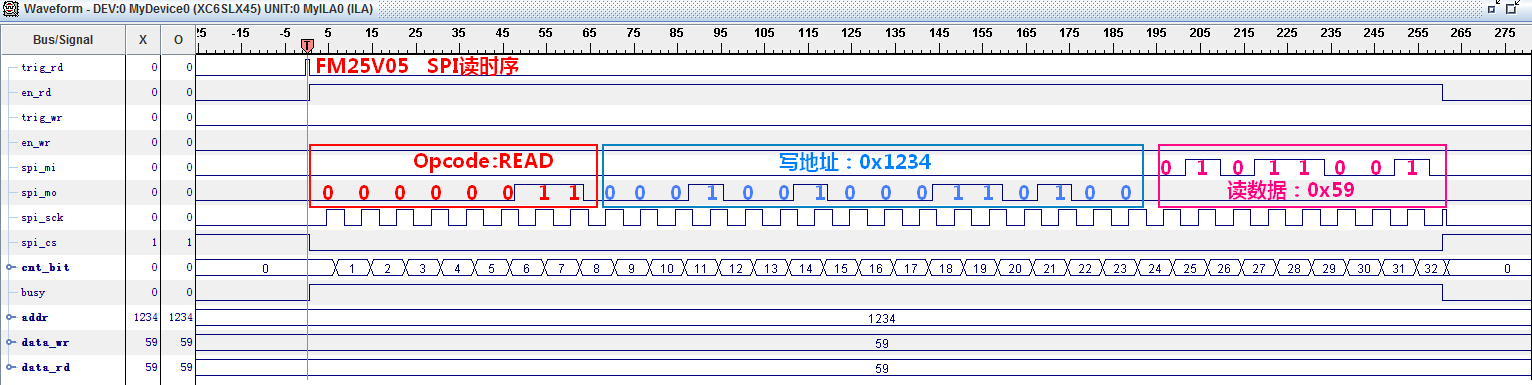

下图的波形是使用Xilinx FPGA对一款铁电存储器FM25V05的驱动,采用标准4线SPI协议,和IIC接口的ERPOM操作方式类似:先写控制字,再写地址,再写数据或者读数据,SCK时钟频率40MHz,使用ChipScope抓取到的实际读写波形,在SCK低电平中间数据改变,在SCK上升沿左右数据要保持稳定。

SPI写时序,需要注意的是先写使能命令,然后重新产生CS信号,这一块卡了好久,在官方示例的C代码中才发现了问题所在,还是对手册上的时序理解不到位。

SPI读时序,先写控制字,再写16位地址,然后读8位数据。

SPI和IIC的对比

- SPI是全双工,而IIC是半双工。

- IIC支持多主机多从机模式,而SPI只能有一个主机。

- 从GPIO占用上来看,IIC占用更少的GPIO,更节省资源。

- SPI的数据位宽更灵活,可以根据需要选择多位数据宽度。

- SPI协议没有响应机制,主机无法得知从机是否接收到所发的数据,如果不采取一些方法的话可能会导致数据丢帧。

- 正是因为没有复杂的响应机制,SPI协议可以做到非常高的速率(上百兆),每一个SCK都可以进行数据的传输,通过引入CRC校验等校验方法,可以即高速传输数据,又能保持数据的准确度。

- IIC通过器件地址来选择从机,从机数量的增加不会导致GPIO的增加,而SPI通过CS选择从机,每增加一个从机就要多占用一个GPIO,当然也可以通过加入译码器来实现多从机控制。

- 两者大多都应用于板内器件短距离通讯。

总结

使用FPGA来实现SPI时序,最大的好处就是灵活,时序可以根据需要精确的定制,可以实现非常高的速率,特别是同时驱动多片芯片上有很大的优势,在一些高速AD采集的场合必须使用FPGA来实现,难点就是做起来比较麻烦,需要一点点的调试,仿真,虽然FPGA也有一些现成的IP可以使用,但还是不够灵活。不像STM32等MCU那样有现成的库函数和寄存器简单几行代码配置一下,就可以实现主从模式、SPI模式、数据位宽、多种速率、单线双线、半双工全双工、DMA等等。总之,FPGA和MCU各有优点,也各有不足,根据需求来选择吧!